#include <dsym.h>

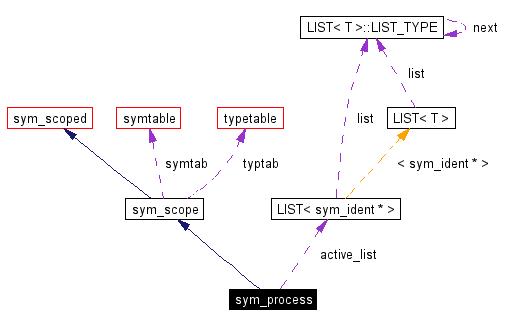

Inheritance diagram for sym_process:

Public Member Functions | |

| sym_process (STRING n) | |

| sym_process () | |

| const uint | get_sy_kind (void) |

Public Attributes | |

| LIST< sym_ident * > | active_list |

A process exists in its parent scope (a component or module) and it may have local variables and functions (e.g., it has a local symbol table). In this sense it is similar to a subprogram. However, unlike a subprogram a process does not have to have a name (although it may have a name associated with it for readability). So a process is not a symbol and can't be looked up in the symbol table.

For simplicities sake the process class is an alias of the sym_scope class, which provides a symbol table and a parent scope pointer.

A process is allocated via the local symbol table, but it is not entered in the symbol table. This is done so that there is a uniform method for allocating all symbol derived objects.

Definition at line 360 of file dsym.h.

|

|

Definition at line 365 of file dsym.h.

00365 : sym_scope( n ) 00366 { 00367 } |

|

|

Definition at line 368 of file dsym.h.

00369 {

00370 }

|

|

|

Reimplemented from sym. Definition at line 372 of file dsym.h. References sy_process, and uint.

00372 { return sy_process; }

|

|

|

|

1.3.3

1.3.3